# Field Stripping a Weapons System: Building a Trustworthy Computer

Dr. Gabriel L. Somlo

## **Document Markings**

Copyright 2019 Carnegie Mellon University.

This material is based upon work funded and supported by the Department of Defense under Contract No. FA8702-15-D-0002 with Carnegie Mellon University for the operation of the Software Engineering Institute, a federally funded research and development center.

The view, opinions, and/or findings contained in this material are those of the author(s) and should not be construed as an official Government position, policy, or decision, unless designated by other documentation.

NO WARRANTY. THIS CARNEGIE MELLON UNIVERSITY AND SOFTWARE ENGINEERING INSTITUTE MATERIAL IS FURNISHED ON AN "AS-IS" BASIS. CARNEGIE MELLON UNIVERSITY MAKES NO WARRANTIES OF ANY KIND, EITHER EXPRESSED OR IMPLIED, AS TO ANY MATTER INCLUDING, BUT NOT LIMITED TO, WARRANTY OF FITNESS FOR PURPOSE OR MERCHANTABILITY, EXCLUSIVITY, OR RESULTS OBTAINED FROM USE OF THE MATERIAL. CARNEGIE MELLON UNIVERSITY DOES NOT MAKE ANY WARRANTY OF ANY KIND WITH RESPECT TO FREEDOM FROM PATENT, TRADEMARK, OR COPYRIGHT INFRINGEMENT.

[DISTRIBUTION STATEMENT A] This material has been approved for public release and unlimited distribution. Please see Copyright notice for non-US Government use and distribution.

This material may be reproduced in its entirety, without modification, and freely distributed in written or electronic form without requesting formal permission. Permission is required for any other use. Requests for permission should be directed to the Software Engineering Institute at permission@sei.cmu.edu.

Carnegie Mellon® is registered in the U.S. Patent and Trademark Office by Carnegie Mellon University.

DM19-1107

Q:

Could you ask a vendor for *full* software *and* hardware *sources* to *any* system or solution contracted by the DoD, *today*?

#### Myth:

"It is no longer possible for a single person to fully understand how a computer works."

# Field Stripping

#### From <u>dictionary.com</u>:

To take apart (a weapon) for cleaning, lubrication, and repair or for inspection

# Field Stripping: What About Modern Weapons Systems?

- artillery

- navigation

- comms

Non-destructive testing & reverse engineering is relatively easy with *software*

less so with *microchips*!

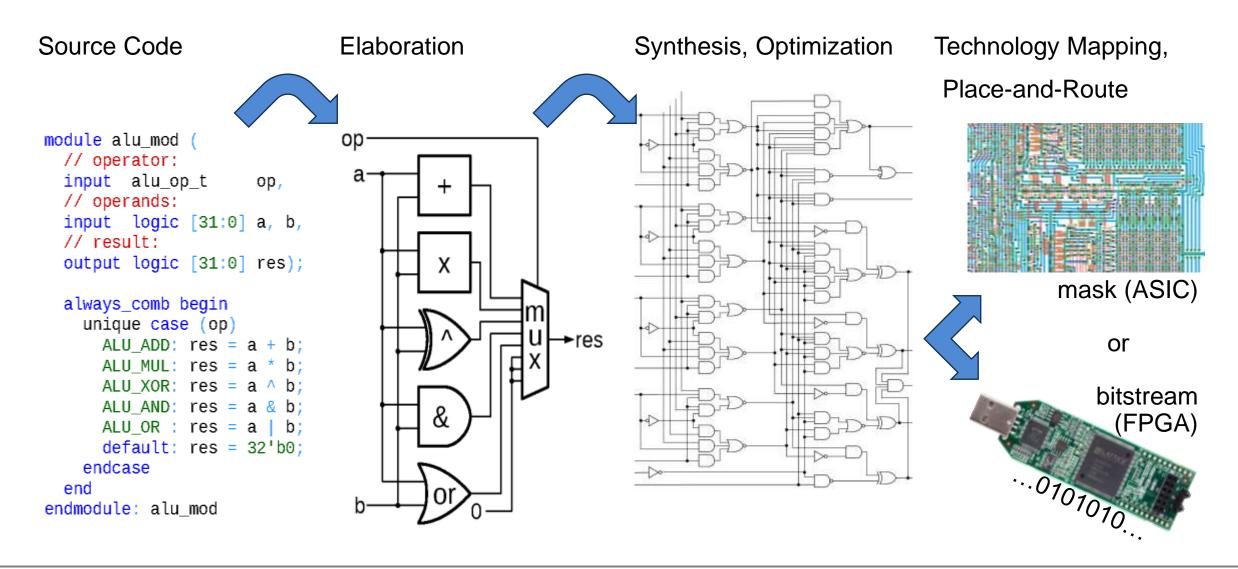

#### Hardware Attack Surface

- ASIC Fabrication (Malicious Foundry)

- masks reverse engineered and modified to insert malicious behavior

- privilege escalation CPU backdoor

- compromised random number generator

- problematic to test/verify after the fact!

- mitigated by using FPGAs instead!

- Compilation (<u>Malicious Toolchain</u>)

- generates malicious design from clean sources

- Design Defects (Accidentally or Intentionally Buggy HDL Sources)

- Spectre

- Meltdown

# Field Stripping a Computer

Applications (incl. compiler)

System Runtime Libraries

Kernel

Hypervisor (optional)

CPU ISA & I/O Registers

Microarchitecture

Register Transfer Level (RTL)

**ASICs**

**FPGAs**

Software (e.g., Linux, BSD, seL4)

Hardware (e.g., x86, ARM, RISC-V)

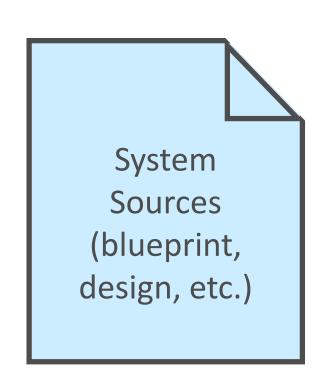

#### Self-hosting:

- a system's capability to produce new versions of itself, from bounded sources, without reliance on external third-party support\*

- the software stack is self-hosting

- \* Assuming the hardware can be trusted!!!

# Field Stripping a Computer

Applications (incl. compiler) System Runtime Libraries Software (e.g., Linux, BSD, seL4) Kernel Hypervisor (optional) CPU ISA & I/O Registers Microarchitecture Hardware (e.g., x86, ARM, RISC-V) Register Transfer Level (RTL) **ASICs FPGAs**

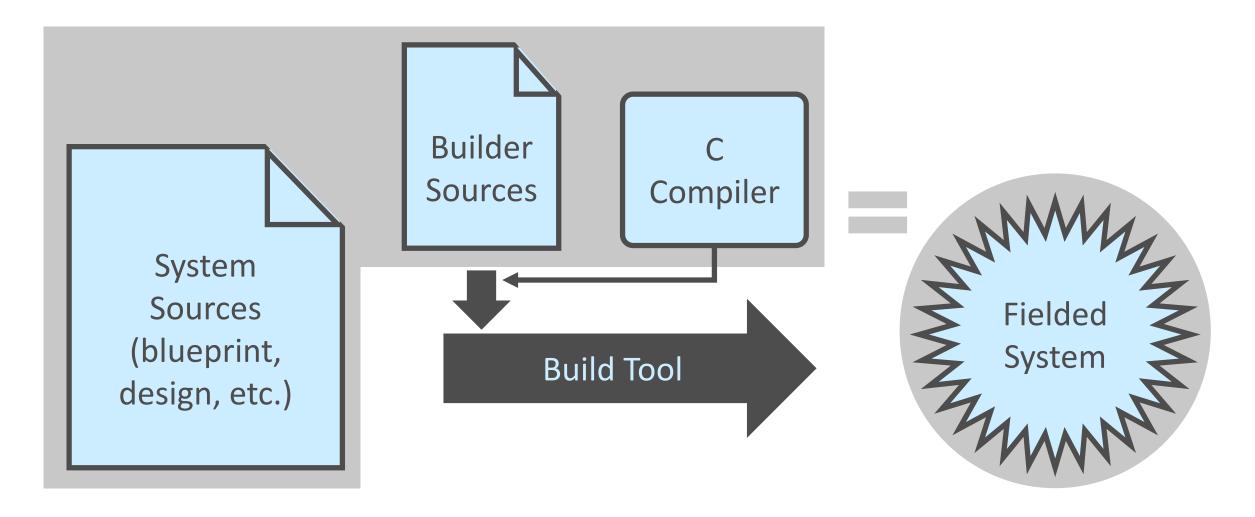

Goal: Extend self-hosting property to encompass hardware, including hardware source-language (HDL) compiler!

#### Self-hosting:

- a system's capability to produce new versions of itself, from bounded sources, without reliance on external third-party support\*

- the software stack is self-hosting

- \* Assuming the hardware can be trusted!!!

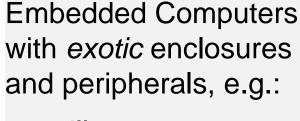

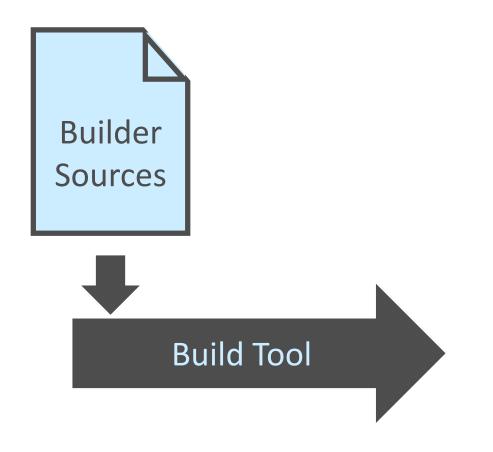

# Hardware Development and Compilation Stages

ASICs vs. FPGAs

- Application Specific Integrated Circuits

- dedicated, optimized etched silicon

- photolithographic masks

- "hard" IP cores

- Field Programmable Gate Arrays

- grid: programmable blocks, interconnect

- bitstream

- "soft" IP cores

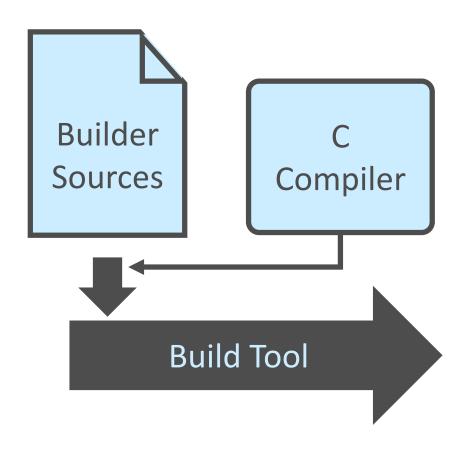

## Bootstrapping a Trustworthy RISC-V Cleanroom System

- [x86/Linux]: Use DDC to verify we have a clean C compiler

- including a rv64 cross-compiler

- [x86/Linux]: Build clean HDL compiler toolchain, for both x86 and rv64

- [x86/Linux]: Cross-compile target rv64 OS (kernel, libraries, utilities)

- [x86/Linux]: Build rv64 SoC FPGA bitstream, from HDL sources

- [rv64/Linux]: Boot up FPGA-based rv64 computer into cross-compiled OS

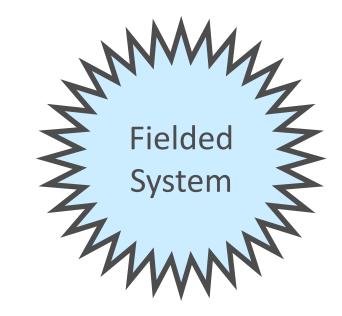

- rv64/Linux system is *self-hosting* from this point forward!

- [rv64/Linux]: Natively rebuild FPGA bitstream, kernel, libraries, and applications

- we now have a trustworthy cleanroom

- guaranteed to "honestly" compile any imported sources (HDL and/or software)!

# List of Ingredients

Physical Hardware: FPGA development board (based on Lattice ECP5 series chip):

Versa-5G or <u>TrellisBoard</u>

Free/Open HDL toolchain (Verilog-to-bitstream):

• Yosys (compiler), Project Trellis (bitstream utilities), NextPNR (place-and-route tool)

Free/Open RISC-V 64-bit CPU:

Rocket Chip

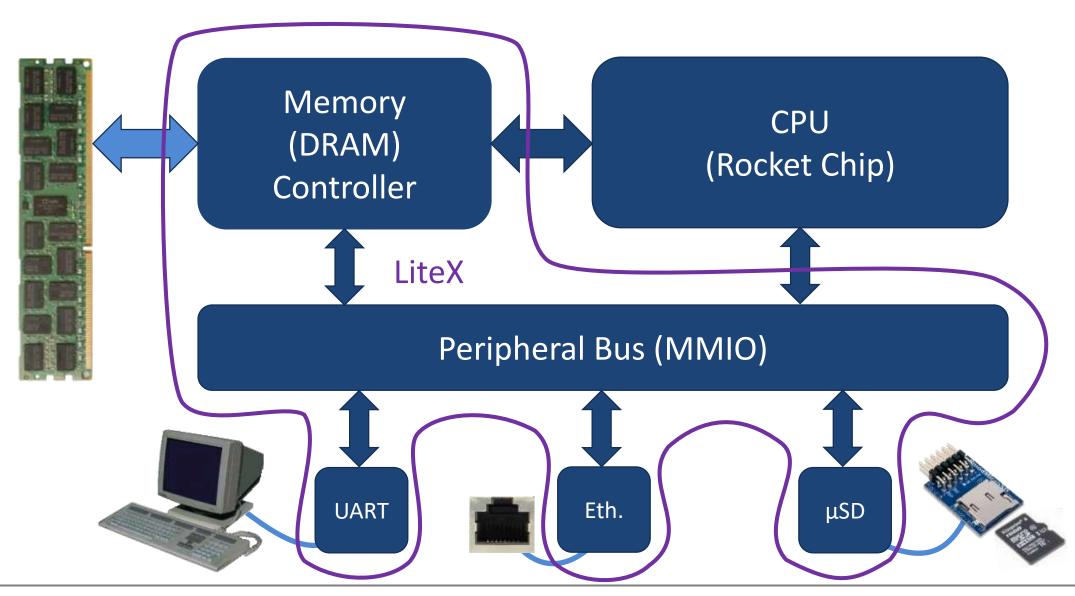

Free/Open system-on-chip (SoC) environment (e.g., system bus, peripherals):

LiteX

Free/Open software stack (e.g., Linux kernel, glibc runtime, GCC compiler):

• Fedora-riscv64

#### LiteX + Rocket 64-bit FPGA-based Linux Computer

# **Next Steps**

NEAR MID FAR Performance Optimizations Formal Analysis & Verification Hardware Assurance BCPs Early prototype HDL is a Starting from a bounded Cyber weapons as target-rich environment set of sources, trustworthy as kinetic, for further performance despite supply chain 100% as trustworthy as complications! the fielded system. improvements, e.g.,: 64bit AXI system bus Goal: measure actual separate RAM and ability to trust the system MMIO data paths by conducting source code analysis!

#### Demo: Linux booting on Rocket+LiteX on ECP5 FPGA

```

(c) Copyright 2012-2019 Enjoy-Digital

(c) Copyright 2007-2015 M-Labs Ltd

BIOS built on Aug 31 2019 22:04:19

BIOS CRC passed (37844d20)

Migen git sha1: -----

LiteX git sha1: 24410f0b

--======= SoC info ===========--

CPU:

RocketRV64[imac] @ 60MHz

ROM:

32KB

SRAM:

4KB

L2:

8KB

MAIN-RAM: 131072KB

--==== Peripherals init =======--

```